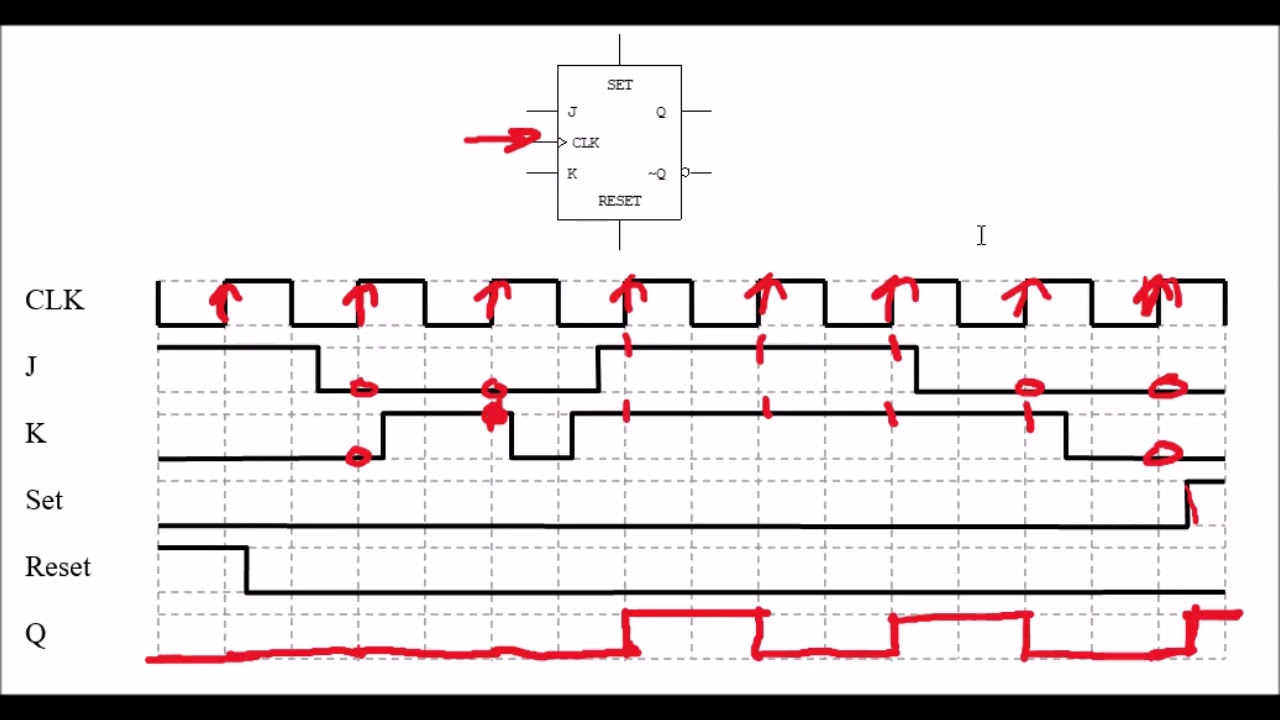

In other words, the output state of a “sequential logic circuit” is a function of the following three states, the “present input”, the “past input” and/or the “past output”. This means that sequential logic circuits are able to take into account their previous input state as well as those actually present, a sort of “before” and “after” effect is involved with sequential circuits. When CK is low, Q will latch onto the last value it had before CK went low, and hold it until CK goes high again.Unlike Combinational Logic circuits that change state depending upon the actual signals being applied to their inputs at that time, Sequential Logic circuits have some form of inherent “Memory” built in. While CK is high, Q will take whatever value D is at. The most common type of latch is the D latch. Latches are similar to flip-flops, but instead of being edge triggered, they are level triggered. The timing diagram for the negatively triggered JK flip-flop: The truth table for a negatively triggered JK flip-flop: The JK flip-flop is usually negative edge triggered. If J and K are both 1, the output is inverted. If J and K are both 0, the output stays the same as it was before. J corresponds to a "set" signal, and K corresponds to a "reset" signal. The JK flip-flop has two inputs, labeled J and K. Timing diagram for the positive edge triggered D flip-flop: (↑ indicates a rising edge on the clock pulse X indicates that it has no effect on outcome) The truth table for a positive edge triggered D flip-flop: The D flip-flop is usually positive edge triggered. The D (Data) flip-flop has an input D, and the output Q will take on the value of D at every triggering edge of the clock pulse and hold it until the next triggering pulse. There are several types of flip-flops but the two most important kind are the D and J-K flip-flops.

Truth Table for CLR and PRE (active low) PRE The symbols used for clear and preset (the bubble indicates an inverted signal):

The CLR and PRE signals can be asserted any time and don't have to be edge triggered they will override any other inputs, including the clock. These inputs are typically inverted, so they are active when the input signal is low ( Active Low Input). Many flip-flops will also have a clear (CLR) and preset (PRE) terminal. The symbols used for positive and negative edge triggering on flip-flops: Flip-flops are edge triggered they either change states when the clock goes from 0 to 1 (positive/rising edge) or when the clock goes from 1 to 0 (negative/falling edge). Because the state of a flip-flop often depends on the previous state of a circuit (for example, the output of one flip flop may be the input to another), and because each flip-flop and logic gate needs a certain amount of time to switch its output, we usually clock the devices, that is, we synchonize all the flip-flops to change states at the same time with a clocked pulse.

0 kommentar(er)

0 kommentar(er)